|

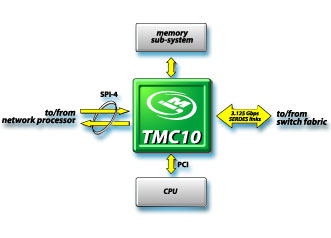

The TMC10 is the industry's first single

chip, wire-speed traffic management co-processor

capable of operating at full duplex 10 Gbps

and OC-192c rates.

Highly

integrated. This highly integrated traffic

management solution performs buffer and

queue management functions, traffic scheduling,

flow control across a switch fabric, congestion

management, and statistics for multiprotocol

traffic at OC-192c line rates. This allows

equipment and network designers to balance

congestion control with quality of service

parameters for a variety of edge, metro

and core network applications.

In addition, the TMC10 includes embedded

on-chip full-duplex serializer/deserializer

(SERDES) links, with optional ECC for reducing

link error rates, for optimal performance

and integration efficiency. A rich feature

set is provided to maximize carrier-class

availability and reliability through support

for various fabric redundancy configurations,

including N+1, N+2, and 1+1redundancy options,

along with zero packet loss fail-over capability.

Flexible.

The TMC10 is based on Internet Machines'

patent-pending Parallel Channel Architecture

(PCA), which allows system designers to

develop high-performance multi-gigabit switches

that can scale in aggregate and per-port

bandwidth capacity, as well as overall system

port density, in flexible increments.

Protocol

and service independent. The

TMC10 allows concurrent traffic management

processing of multiprotocol and multiservice

traffic.

Interoperable.

The TMC10 interoperates with Internet Machines'

SE200 protocol-independent switch element

or with other switch fabric solutions. To

interface to a network processor or other

co-processors, the TMC10 supports the Optical

Internetworking Forum's SPI-4 Phase 2 Implementation

Agreement.

|