The SE200 is the highest capacity, single-chip switch

element available today. A single chip delivers

200 Gbps of switching capacity, and larger fabrics

using multiple SE200 devices in parallel are able

to deliver terabit speeds. Sixty-four embedded serializer-deserializer

(SERDES) transceivers optimize performance and integration

efficiency in backplane and shelf-to-shelf interconnection

schemes.

The SE200 is the highest capacity, single-chip switch

element available today. A single chip delivers

200 Gbps of switching capacity, and larger fabrics

using multiple SE200 devices in parallel are able

to deliver terabit speeds. Sixty-four embedded serializer-deserializer

(SERDES) transceivers optimize performance and integration

efficiency in backplane and shelf-to-shelf interconnection

schemes.

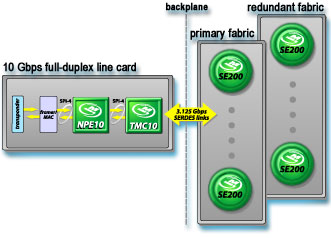

The

SE200 is based on Internet Machines' patent-pending

Parallel Channel Architecture (PCA), which allows

system designers to develop high-performance multi-gigabit

switches that can scale in aggregate and per-port

bandwidth capacity, as well as overall system

port density, in flexible increments. The primary

function of the SE200 is to provide high-speed

switching between a source and destination port,

supporting multiple network interfaces or line

cards. Through its innovative virtual link aggregation

capability, the SE200 supports switching for multiple

concurrent protocols and services for any size

packet at any data rate from OC-48c to OC-768c.

For high-end switching applications, multiple

SE200's can be designed into a single stage topology

to scale fabric capacities to 1.2 Terabits per

second.

Highly

integrated. Single chip, 64 x 64 port, non-blocking,

self-routing, buffered crossbar switch element

delivers 200 Gbps switching capacity, and a fabric

using multiple SE200 devices can deliver terabit

speeds. Integrated full duplex SERDES transceivers,

with optional ECC for reducing link error rates,

optimizes performance and increases integration.

Concurrent protocol independent, multiservice

support. The SE200 allows concurrent switching

of multiprotocol and multiservice traffic.

Flexible.

Flexible architecture scales up to 1.2 Tbps of

non-blocking switching capacity with up to 64

line cards, each supporting traffic throughput

of up to 10 Gbps/OC-192c, using multiple switch

elements in parallel. Larger fabrics and port

densities can be supported in the future using

multi-stage topologies.

Features

and Benefits

|

|

- Performs

both variable-length or fixed-length

PDU switching

- All

ports include on-chip embedded

full-duplex SERDES links,

with optional ECC for reducing

link error rates, for optimal

performance and integration

efficiency

- Provides

an on-chip SRAM buffer for

storing and scheduling packets

during temporal congestion

in the fabric, eliminating

the need for external components

in the fabric subsystem

- Connects

directly to Internet Machines'

TMC10 traffic manager, or

interworks with other traffic

management solutions

- No

synchronization required between

different links or different

switching elements, simplifying

design of backplanes and multi-shelf

systems

- Distributed

architecture allows for N+1,

N+2, and 1+1 redundancy options,

with zero packet loss fail-over

capability to maximize carrier-class

availability and reliability

- Programmable

association between logical

port numbers and physical

links and auto link diagnostics

allow simple rerouting of

traffic to bypass link failures

-

Supports separate CRC validations

to check header integrity

independently from payload

integrity

-

Supports spatial multicasting

-

Provides a dedicated high

priority in-band messaging

path, allowing for flexible

flow control schemes between

ingress and egress line cards

to manage traffic flow across

the fabric subsystem

-

Offers flexible fabric configuration

andmanagement capabilities

-

Memory BIST, JTAG (IEEE P1149.1

standard), and scan function

|

|

|

|

|

|